clock 은 PLL (Phase Locked Loop)을 통해 일정 주파수 generation

PLL : TCXO (기준주파수) > 원하는 주파수 clock generation

10 MHz TCXO : taget의 clock source

>

Fout : 100MHZ

VCO (voltage controlled Oscillator ) : 원하는 주파수를 전압을 통해 만들어냄

// 전압 up : 101 MHZ 이런식

Phase Detector : VCO sampling > TCXO 와 같은 level 로 낮춘뒤 ( I/IO Divider)

위상의 차이를 구별함

> 다시 100MHz 로 잘나오는지 확인하기 위함

> 만약 오차가나면

펄스 ->전압 변환기 : VCO 의 input 전압 재조정

: 위상이 빠르면 느리게 하는등

on-chip PLL : 안정적인 주파수를 내는 FFS ( Fixed Frequnecy Source)

>> CPLL, HPLL, PPLL

: TCXO 로 부터 온 주파수를 안정적으로 clock을 만들어내 전체 IP들에게 전달

까만선 : Data Bus

화살표 : clcock

Counter : clock Counting

ex)

/2 : 클럭이 2번들어오는걸 카운트 한뒤 output

> 한가지 주파수를 가지고 여러 주파수를 만들어 각 peripheral 에 맞는 주파수 공급

M/N:D counter : PLL 안에 counter 를 넣어 더욱 다양하게

1/M divider : Fout 을 1/M배 함

>

M 이 커질수록 Fout 도 커져야함

>>

VCO ouput 을 더 큰 주파수로 낼 수 있게됨

>>> TCXO M배한셈

+

TCXO 1/N counter 이용 > VCO 값이 1/N 이 됨

>>

VCO 값을 M배, 1/N배

>>>

M/N counter PLL

이렇게 만들어낸 Fout 을 TCXO 로 다시연결해서 또 변경할 수 있음

N과 M을sw 로 변경가능한 clock controller 를 갖는 MCU 가 있음

> Register 로 설정

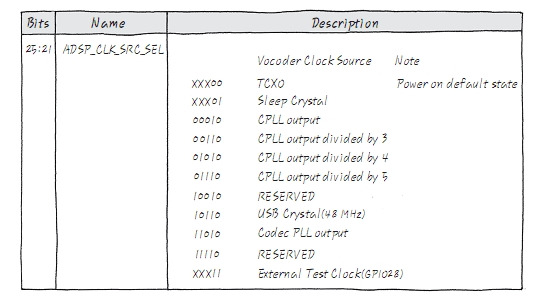

> source selection

> ADSP 의 source clock 을 CPLL의 ouput에 1/3배 clock을 넣어야 하는경우

: [25:21] bit 를 00110 으로 설정

Duty : clock 이 High / Low 주기성을 가짐 > High 를 따로 설정

>>

M/N + Duty 까지 control 가능한 clock controller

== M/N:D counter

'임베디드 > 임베디드 레시피' 카테고리의 다른 글

| MMU : Memory Management Unit ( 다시보기) (0) | 2025.01.16 |

|---|---|

| Cache, Cash (0) | 2025.01.16 |

| Wait State (0) | 2025.01.15 |

| Synchronous ,Asynchronous (0) | 2025.01.15 |

| MACRO Technics (0) | 2025.01.14 |